Just as Multiplexer, Decoder is also a Combinational circuit which transforms given inputs to a maximum number of outputs (maximum outputs equal to 2n and n are given inputs ).

Compose a 4×16 decoder with enable from 2×4 decoders with enable. Step-by-step solution: Chapter: CHB CH1 CH2 CH3 CH4 CH5 CH6 CH7 CH8 CH9 Problem: 1E 2E 3E 4E 5E 6E 7E 8E 9E 10E 11E 12E 13E 14E 15E 16E 17E 18E 19E 20E 21E 22E 23E 24E 25E 26E 27E 28E 29E 30E 31E 32E 33E 34E 35E 36E 37E 38E 39E 40E 41E 42E 43E 44E 45E 46E 47E 48E 49E 50E 51E.

3 to 8 Decoder: Verilog Code in Dataflow Modeling: module decoder3to8( input 2:0 a, output 7:0 d ); assign d. Decade counter Block diagram for Decade counter: Verilog code for Decade Counter/ MOD-10 Counter: (Behavioural model) module decade. Verilog tutorial and programs with Testbench code - 3 to 8 decoder. Using only three 2-to-4 decoders with enable and no other additional gates, implement a 3-to-8 decoder with enable. The inputs of the resulting 3-to-8 decoder should be labeled X2.0 for the code input and E for the enable input. The outputs should be labeled Y7.0. Here's my current solution.

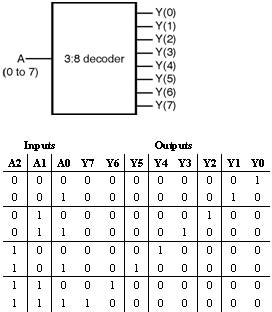

A block diagram of decoder consists of input lines, one or more enable inputs and a maximum number of output lines.

To construct a decoder, we require to know the number of all possible output lines that totally depends on the given input.

To construct a decoder, we require to know the number of all possible output lines that totally depends on the given input.

So, if n represents given input lines then possible output lines would be 2n.

Decoder with three inputs would give 8 outputs (n=2,23 that is 8).

Decoder with three inputs would give 8 outputs (n=2,23 that is 8).

3x8 Decoder Vhdl Code Examples

Here are the steps to construct 3 to 8 decoder

Step 1. Now we know possible outputs for 3 inputs, so construct 3 to 8 decoder, having 3 input lines, a enable input and 8 output lines. In the below diagram, given input represented asI2, I1 and I0 , all possible outputs named as O0, O1, O2,O3, O4, O5,O6& O7 and a E were represented by Enable input.

3 To 8 Decoder With Enable Vhdl Code

With Enable input

Without Enable input

Step 2. Now, it turns to construct the truth table for 3 to 8 decoder. E input can be considered as a control input. Mean to say, If E equals to 0 then the decoder would be considered as disabled regardless of what inputs are, If E equals to 1 then the decoder would work as per inputs.

Truth table without E input

| Inputs | Outputs | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| I2 | I1 | I0 | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

We can represent the following output as:

O0 = I0‘.I1‘.I2‘

O1 = I0.I1‘.I2‘

O1 = I0.I1‘.I2‘

O2 = I0‘.I1.I2‘

O3 = I0.I1.I2‘

O4 = I0‘.I1‘.I2

O5 = I0.I1‘.I2

O6 = I0‘.I1.I2

O7 = I0.I1.I2

O3 = I0.I1.I2‘

O4 = I0‘.I1‘.I2

O5 = I0.I1‘.I2

O6 = I0‘.I1.I2

O7 = I0.I1.I2

Truth table with E input

| Inputs | |||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| E | I2 | I1 | I0 | O7 | O6 | O5 | O4 | O3 | O2 | O1 | O0 |

| 0 | - | - | - | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Decoder with E

Explanation:

In above diagram, there were three input lines along with their complements using Inverters. Each and every AND gate were holding four inputs from E, I1, I1 and I0 and producing 8 outputs.

3x8 Decoder Truth Table

Decoder Without E

Explanation:

In the above diagram, there were three input lines with their respective complements using Inverters. Each and every AND gate were holding three inputs from I1, I1 and I0 and producing 8 outputs.

In the above diagram, there were three input lines with their respective complements using Inverters. Each and every AND gate were holding three inputs from I1, I1 and I0 and producing 8 outputs.